### Code No. : 14405

# VASAVI COLLEGE OF ENGINEERING (Autonomous), HYDERABAD B.E. (CBCS: ECE) IV-Semester Main Examinations, May-2018

### **Pulse, Digital and Switching Circuits**

Time: 3 hours

Max. Marks: 70

Note: Answer ALL questions in Part-A and any FIVE from Part-B

## Part-A $(10 \times 2 = 20 \text{ Marks})$

- 1. How does an RC Low Pass filter behaves when RC>>T? Write the output expression for LPF.

- 2. Draw a clipper circuit to allow the part of input sine wave if input is greater than 2V?

- 3. Write the applications of Schmitt trigger?

- 4. What are the drawbacks of direct coupled binary circuit?

- 5. Simplify the given boolean function F = A+AB+ABC+...

- 6. Why NAND and NOR gates are known as universal gates? Justify.

- 7. Distinguish between combinational and sequential circuits.

- 8. Write the excitation tables for SR and JK Flip-Flops.

- 9. What is race around condition? When and why does it occur?

- 10. List out the architectural features of Mealy and Moore machines.

#### Part-B $(5 \times 10 = 50 \text{ Marks})$

- 11. a) Explain the operation of Compensated attenuator.

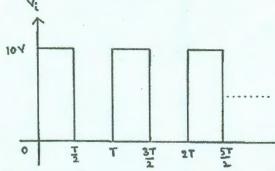

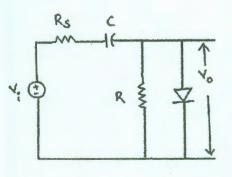

- b) A square wave with amplitude 10Volts and repetition frequency 10 kHz is applied to the following circuit with circuit parameters given by

$R_s = R_f = 100\Omega, R = 20K\Omega, C = 1\mu F, V_{\gamma} = 0.$

Determine the output voltage waveform for few cycles and indicate its voltage levels.

ŀ

- 12. a) Explain the operation of emitter coupled binary circuit and derive the necessary [6] expressions with a neat sketch.

- b) Show that an astable multivibrator can be used as a voltage to frequency converter. [4]

- 13. a) Simplify the following Boolean expression for minimal POS form using K-map and [6] implement using NOR gates.  $F(w, x, y, z) = \pi M(4,5,6,7,8, 12) + \pi d(1,2,3,9,11,14)$ .

- b) Minimize the given function using K-map and for minimized function draw its logic [4] diagram using NAND gates.

$F(a, b, c, d) = \Sigma m (0, 1, 2, 3, 4, 8, 9, 12).$

[5]

[5]

| 14. a) Convert the following Flip-I                                               | Flops                                                                                                                                           | [5]        |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| i) D to SR Flip- Flop                                                             | ii) D to JK Flip- Flop.                                                                                                                         |            |

|                                                                                   | function F (a, b, c, d) = $\Sigma$ m (0, 1, 2, 3, 4, 8, 9, 12).<br>ii) 4×1 multiplexer                                                          | [5]        |

| 15. a) Design a mod-6 synchronou                                                  | s counter using JK Flip-Flops.                                                                                                                  | [7]        |

| b) List out the merits and deme                                                   | $\mathcal{L}^{\alpha}(\mathcal{A}) = \mathcal{L}^{\alpha}(\mathcal{A}) + \mathcal{L}^{\alpha}(\mathcal{A}) = \mathcal{L}^{\alpha}(\mathcal{A})$ | [3]        |

| 16. a) Derive an expression for fre                                               | equency of UJT Relaxation Oscillator.                                                                                                           | [5]        |

| b) Explain the operation of Hig                                                   | gh Pass RC circuit to an exponential input.                                                                                                     | [5]        |

| 17. Answer any two of the following                                               | ng:                                                                                                                                             |            |

| a) Full subtractor using only 2                                                   | input NAND gates                                                                                                                                | [5]        |

| <ul><li>b) 4-bit adder/subtractor</li><li>c) 3-bit twisted ring counter</li></ul> |                                                                                                                                                 | [5]<br>[5] |

| c) 5-on twisted mig counter                                                       |                                                                                                                                                 | [2]        |

|                                                                                   | ଔଔଷ୍ଟରାହା                                                                                                                                       |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

|                                                                                   |                                                                                                                                                 |            |

Minemure the proof function using K-map and for minimized function draw its male disgram using NAND gates.

(2) 是法人, (1, 1, 1) m2 ~ (0, 2, 3, 4)